# アーリィ / レイト・ゲート・シンクロナイザ・メガファンクション

Solution Brief 17

June 1997, ver. 1

ターゲット・アプリケーション： 特長

通信、

デジタル信号処理

ファミリ：

FLEX 10K、FLEX 8000

ベンダ：

Nova Engineering, Inc.

5 Circle Freeway Drive

Cincinnati, OH 45246

Tel. (513) 860-3456

Fax (513) 860-3535

E-mail sales@nova-eng.com

WWW http://www.nova-eng.com

- 完全なクローズド・ループのシンクロナイザ

- ループ・フィルタの帯域が可変

- バランスド・ゲート / デュアル・インテグレータを採用したデザイン

- Altera® の FLEX® 10K デバイスと FLEX 8000 デバイスのアーキテクチャに最適化

- アプリケーション

- デジタル・レシーバ

- Phase-locked loop (PLL)

## 概要

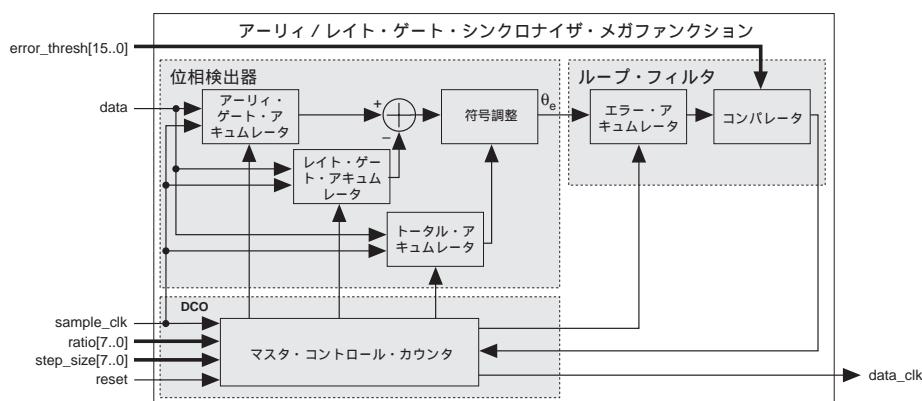

このアーリィ / レイト・ゲート・シンクロナイザのメガファンクションには、1 次元のクローズド・ループ・シンクロナイザに要求されるすべての機能が含まれています。このシンクロナイザは、フェーズ・ディテクタ（位相検出器）、アップ / ダウン・カウンタ・ループ・フィルタ、デジタル制御発振器（DCO）の各部によって構成されています。フェーズ・ディテクタ部にはデュアルのインテグレータを使用したバランスド・アーリィ / レイト・ゲートが構成されています。フェーズ・ディテクタの出力は、データ・クロックと入力データとの間に生じる差分またはフェーズ・エラーとなっています。フェーズ・ディテクタから出力されるフェーズ・エラー ( $\theta_e$ ) は、アップ / ダウン・カウンタでアキュムレートされ、その値はエラーの量と符号によってインクリメントまたはディクリメントされます。

エラー・アキュムレータの値が設定されているエラーのスレッショルドを超えた場合は、DCO が内部で生成されたデータ・クロックの位相を進めたり、遅らせたりして調整します。エラーのスレッショルドはプログラム可能となっており、ループ・フィルタの帯域をコントロールすることができます。ループの帯域幅はエラー・スレッショルドのレベルを上げることにより狭められ、エラー・スレッショルドのレベルを下げることで広げられます。エラー・スレッショルドのレベルが低い程、フィルタは位相エラーの急激な変化にも反応することができます。

また、DCO は内部生成されるデータ・クロックの位相をプログラマブルなステップ・サイズで調整することができます。この位相調整のためのステップ・サイズまたは量は、ループ・アキュムレーション・タイムとデータ・クロックのジッタを決定します。ステップ・サイズを大きくすると、大きな位相エラーを迅速に訂正することができるため、最小のアキュムレーション・タイムが実現されます。また、ステップ・サイズを小さくすることで、ループがロックしているときのクロック・ジッタを最小にすることができます。

図1 アーリィ / レイト・ゲート・シンクロナイザ・メガファンクションのブロック図

## 機能説明

入力されるバイナリ・データをサンプリングするためには、フェーズ・ディテクタに高速のクロックが必要になります。サンプリング・クロックはデータ・レートの偶数倍となる必要があります、通常はデータ・レートの 16 倍 ( $\text{ratio}[7..0] = 16$ ) になります。データとサンプリング・クロックとの関係は下記の式で表されます。

$$T_{\text{data\_clk}} = \text{ratio}[7..0] \times T_{\text{sample\_clk}}$$

ここで  $T_{\text{sample\_clk}}$  = サンプリング・クロックの周期

$T_{\text{data\_clk}}$  = データ・クロックの周期

$\text{ratio}[7..0]$  = 4 から 254 までの整数

マスター・カウンタはデータ・クロックを生成し、アーリイ・ゲートとレイト・ゲートにタイミング・パルスを供給します。アーリイ・タイミング・ゲートでは、シンボル周期の最初の半分の期間で入力信号のエネルギーを積算するアキュムレータをイネーブルにします。レイト・タイミング・ゲートでは、シンボル周期の残り半分の期間で入力信号の信号エネルギーを積算する 2 つ目のアキュムレータをイネーブルにします。そして、トータル・アキュムレータがシンボル周期全体の信号エネルギーを積算します。また、トータル・アキュムレータでは、データ・ビットがバイナリの 1か0かを判定し、位相エラーの符号を適切に調整します。データの過渡期を想定した場合、アーリイ・ゲート・インテグレータとレイト・ゲート・インテグレータとの差は、レシーバの位相エラー ( $\theta_e$ ) の量に比例します。フェーズ・ディテクタの出力は下記の式で表されます。

$$\theta_e = |\sum_{\text{early}}| - |\sum_{\text{late}}|$$

$$\text{ここで } |\sum_{\text{early}}| \leq \frac{\text{ratio}[7..0]}{2} \text{ および } |\sum_{\text{late}}| \leq \frac{\text{ratio}[7..0]}{2}$$

位相エラーは下記の条件になるまでアキュムレートされます。

$$|\sum \theta_e| > \text{error\_thresh}[15..0]$$

アキュムレートされたエラーが、プログラムされているエラー・スレッショルドを超えた場合には、DCO が内部で生成されたデータ・クロックの位相を進めたり、遅らせたりします。訂正される量は  $\text{step\_size}[7..0]$  にプログラムされた値によって決定され、位相調整の方向はアキュムレートされた位相エラーの符号によって決定されます。

DCO による位相訂正または位相ステップは、データ・クロックの位相角またはサイクル全体に対する割合で表すことができます。次式は位相ステップを角度で表す場合の計算方法を示したものです。

$$\text{位相ステップ} = \frac{\text{step\_size}[7..0]}{\text{ratio}[7..0]} \times 360^\circ$$

$\text{step\_size}[7..0]$  の値は、 $\text{ratio}[7..0]$  の値に比較して常に非常に小さな値となります。また、位相訂正の量が  $\text{ratio}[7..0]$  の値より大きくなると、ループは不安定な状態となってしまいます。位相訂正が不必要的場合を除き、 $\text{step\_size}[7..0]$  は 0 よりも大きな値に設定する必要があります。 $\text{step\_size}[7..0]$  の値を 0 に設定すると、シンクロナイザをディセーブルしたことと同じ結果になります。

データ・クロックの位相調整によって発生するタイミング・ジッタは、次の式で計算することができます。

$$\text{timing jitter} = \text{step\_size}[7..0] \times T_{\text{sample\_clk}}$$

## ポート

マスター・コントロール・ロジックはratio[7..0]入力を使用してシンボル当たりのサンプル・クロック数、アーリイ・ゲート当たりのサンプル・クロック数、レイト・ゲート当たりのサンプル・クロック数を決定します。アーリイ・ゲート・インテグレータとレイト・ゲート・インテグレータの積算時間は、ratio[7..0]/2の値で決定されます。フェーズ・ディテクタでは、アーリイ・ゲート・インテグレータとレイト・ゲート・インテグレータの積算時間が等しくなっている必要があります。このため、ratio[7..0]の値は4から254までの整数で、偶数となっている必要があります。表1はアーリイ/レイト・ゲート・シンクロナイザ・メガファンクションのポートを示したものです。

表1 アーリイ/レイト・ゲート・シンクロナイザ・メガファンクションのポート

| ポート名                | タイプ | ビット幅 | 機能                                    |

|---------------------|-----|------|---------------------------------------|

| data                | 入力  | 1    | データ・クロックの1サイクル分と等しいビット周期を持つバイナリの入力データ |

| sample_clk          | 入力  | —    | サンプル・クロック                             |

| reset               | 入力  | —    | 非同期リセット、アクティブHigh                     |

| ratio[7..0]         | 入力  | 8    | データ・クロック当たりのサンプル・クロック数を設定             |

| error_thresh[15..0] | 入力  | 16   | 位相訂正が生じるエラー・スレッショルドの設定                |

| step_size[7..0]     | 入力  | 8    | 位相訂正の量を設定                             |

| data_clk            | 出力  | —    | 入力データに位相が同期した出力クロック                   |

ratio[7..0]、error\_thresh[15..0]、step\_size[7..0]の値を変更する場合は、sample\_clkに同期させて行う必要があります。特に、これらの値はsample\_clkの立ち上がりクロックで安定している必要があります。

## デバイスの使用効率

アーリイ/レイト・ゲート・シンクロナイザ・メガファンクションは、FLEX 10KとFLEX 8000用に設計されていますが、FLEX 10Kのエンベデッド・アレイ・ブロック(EAB)は使用されていません。このため、このメガファンクションは双方の製品ファミリーで同じように高い性能を発揮します。表2は、このシンクロナイザの最大動作クロック周波数とデバイスの使用効率を示したものです。

表2 標準的なデバイスの使用効率

| 設計時の設定                                                               | クロック( $f_{MAX}$ ) | ロジック・セル数 | EAB数 |

|----------------------------------------------------------------------|-------------------|----------|------|

| error_thresh[15..0] = 任意<br>ratio[7..0] = 任意<br>step_size[7..0] = 任意 | 35 MHz            | 260      | 0    |

## アプリケーション

このアーリイ/レイト・ゲート・シンクロナイザ・メガファンクションは、基本的に「Digital Phase-Locked Loop(DPLL)」となっています。このシンクロナイザは、内部生成されたデータ・クロックと入力データ間の位相ロック機能を実現するようにデザインされたものです。さらに、2つのクロック間の位相ロックを行うような基本的な機能も提供しています。

入力データをリファレンス・クロックに接続することにより、このシンクロナイザをPLLとして使用することもできます。このときのリファレンス・クロックは、シンクロナイザに対して1と0の交互に繰り返されるパターン(101010など)として入力されます。また、内部タイミングやコントロール信号を生成には、高速のサンプリング・クロックが必要です。データ・クロックはリファレンス・クロックの2倍の周波数になっているため、出力データ・クロックを2分周する必要があります。

---

## 日本アルテラ株式会社

〒163-04 東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL. 03-3340-9480 FAX. 03-3340-9487

Copyright ©1997 Altera Corporation. AlteraAMPP、FLEX、FLEX 10K、FLEX 8000は Altera Corporationの米国および該当各国における trademark または service markです。他のブランド、製品名は該当各社の trademark です。この資料に掲載されている情報、規格などは予告なく変更される場合があります。Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. All rights reserved.